FPGA自主設(shè)計(jì)CPU與計(jì)算機(jī)制作全攻略 從硬件開(kāi)發(fā)到資源獲取

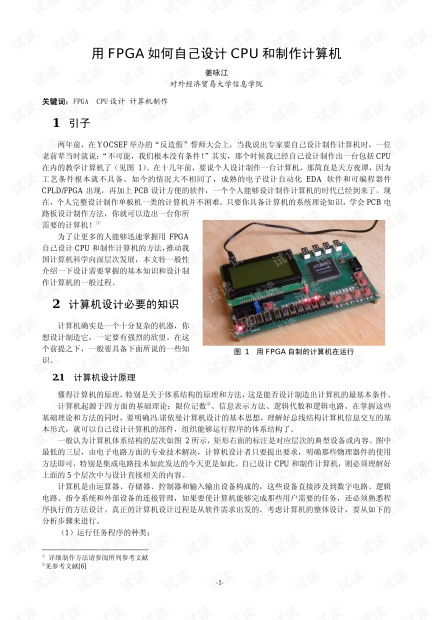

隨著集成電路技術(shù)的飛速發(fā)展,現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)因其高度的靈活性和可重構(gòu)性,已成為硬件開(kāi)發(fā)者和計(jì)算機(jī)體系結(jié)構(gòu)學(xué)習(xí)者的理想平臺(tái)。利用FPGA自主設(shè)計(jì)CPU并構(gòu)建完整的計(jì)算機(jī)系統(tǒng),不僅能深化對(duì)計(jì)算機(jī)底層原理的理解,還能培養(yǎng)從硬件設(shè)計(jì)到系統(tǒng)集成的綜合能力。本文將系統(tǒng)性地介紹基于FPGA的CPU設(shè)計(jì)流程、計(jì)算機(jī)制作要點(diǎn),并推薦相關(guān)的硬件開(kāi)發(fā)文檔與資源,特別是國(guó)內(nèi)開(kāi)發(fā)者常用的CSDN等平臺(tái)上的寶貴資料。

一、FPGA設(shè)計(jì)CPU的核心步驟

- 確定指令集架構(gòu)(ISA):這是CPU設(shè)計(jì)的起點(diǎn)。初學(xué)者可從精簡(jiǎn)指令集(如MIPS、RISC-V)入手,因其設(shè)計(jì)相對(duì)簡(jiǎn)潔,社區(qū)資源豐富。確定指令格式、尋址模式、寄存器組和基本操作(如算術(shù)邏輯運(yùn)算、加載存儲(chǔ)、分支跳轉(zhuǎn))。

- 微架構(gòu)設(shè)計(jì)與模塊劃分:根據(jù)ISA,將CPU劃分為若干功能模塊,例如:

- 取指單元(IF):從指令存儲(chǔ)器讀取指令。

- 譯碼單元(ID):解析指令,生成控制信號(hào)。

- 執(zhí)行單元(EX):執(zhí)行算術(shù)邏輯運(yùn)算。

- 訪(fǎng)存單元(MEM):處理數(shù)據(jù)存儲(chǔ)器的讀寫(xiě)。

- 寫(xiě)回單元(WB):將結(jié)果寫(xiě)回寄存器堆。

設(shè)計(jì)數(shù)據(jù)通路和控制單元,可采用單周期、多周期或流水線(xiàn)結(jié)構(gòu),流水線(xiàn)能顯著提升性能但復(fù)雜度更高。

- 硬件描述語(yǔ)言(HDL)實(shí)現(xiàn):使用Verilog或VHDL編寫(xiě)各模塊的代碼。這是將設(shè)計(jì)“固化”的關(guān)鍵步驟。務(wù)必注意代碼的可綜合性和時(shí)序約束,例如避免組合邏輯環(huán)路,合理處理時(shí)鐘與復(fù)位信號(hào)。

- 仿真與驗(yàn)證:在綜合到FPGA之前,必須進(jìn)行充分的仿真測(cè)試。使用如ModelSim等工具,編寫(xiě)測(cè)試平臺(tái)(Testbench),對(duì)每條指令、各種邊界情況進(jìn)行模擬,確保功能正確。這是調(diào)試和保證設(shè)計(jì)可靠性的核心環(huán)節(jié)。

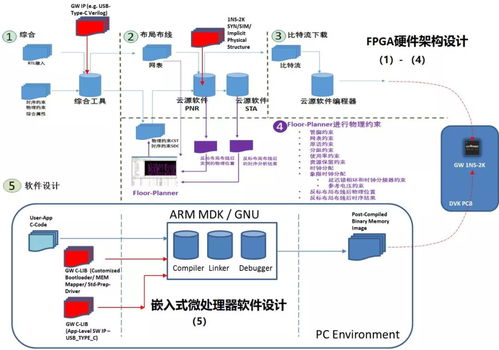

- 綜合、布局布線(xiàn)與下載:使用FPGA廠(chǎng)商的開(kāi)發(fā)工具(如Xilinx的Vivado、Intel的Quartus)進(jìn)行綜合,將HDL代碼轉(zhuǎn)換為門(mén)級(jí)網(wǎng)表,再通過(guò)布局布線(xiàn)映射到FPGA的具體邏輯資源上,最后生成比特流文件并下載到FPGA開(kāi)發(fā)板中。

二、擴(kuò)展為完整計(jì)算機(jī)系統(tǒng)

一個(gè)完整的計(jì)算機(jī)除了CPU,還需要外圍設(shè)備和支持系統(tǒng)運(yùn)行的軟硬件環(huán)境:

- 存儲(chǔ)器系統(tǒng):設(shè)計(jì)或調(diào)用IP核實(shí)現(xiàn)指令存儲(chǔ)器(ROM)和數(shù)據(jù)存儲(chǔ)器(RAM)。可進(jìn)一步添加緩存(Cache)以提升性能。

- 輸入輸出(I/O)接口:集成UART(串口)、GPIO、VGA顯示控制器、PS/2鍵盤(pán)鼠標(biāo)接口等,使計(jì)算機(jī)能與外界交互。這些通常通過(guò)總線(xiàn)(如Wishbone、AXI)與CPU連接。

- 總線(xiàn)與互連:設(shè)計(jì)或采用現(xiàn)有片上總線(xiàn),用于連接CPU、內(nèi)存和各類(lèi)外設(shè),管理它們之間的數(shù)據(jù)通信。

- 啟動(dòng)與中斷:實(shí)現(xiàn)啟動(dòng)引導(dǎo)程序(Bootloader)和中斷控制器,使CPU能夠響應(yīng)外部事件,運(yùn)行更復(fù)雜的軟件。

- 軟件生態(tài):為自主設(shè)計(jì)的CPU移植或編寫(xiě)編譯器(如GCC)、匯編器、鏈接器以及基本的操作系統(tǒng)內(nèi)核(如簡(jiǎn)單的實(shí)時(shí)內(nèi)核),形成完整的軟硬件協(xié)同開(kāi)發(fā)環(huán)境。

三、硬件開(kāi)發(fā)文檔類(lèi)資源獲取與學(xué)習(xí)建議

在學(xué)習(xí)和開(kāi)發(fā)過(guò)程中,高質(zhì)量的文檔、教程和開(kāi)源項(xiàng)目至關(guān)重要。國(guó)內(nèi)開(kāi)發(fā)者可以重點(diǎn)關(guān)注以下資源渠道:

- CSDN下載與博客社區(qū):

- 搜索關(guān)鍵詞:在CSDN站內(nèi)搜索“FPGA CPU設(shè)計(jì)”、“RISC-V FPGA”、“計(jì)算機(jī)組成原理實(shí)驗(yàn)”、“Verilog CPU源碼”、“硬件開(kāi)發(fā)文檔”等,可以找到大量博文、課程筆記、實(shí)驗(yàn)報(bào)告和工程代碼壓縮包。

- 精選資源示例:

- 《基于FPGA的簡(jiǎn)易CPU設(shè)計(jì)與實(shí)現(xiàn)》系列博文:通常包含詳細(xì)的設(shè)計(jì)思路和代碼分析。

- 《計(jì)算機(jī)組成原理課程設(shè)計(jì)》相關(guān)資源:許多高校將FPGA設(shè)計(jì)CPU作為課程設(shè)計(jì),其文檔和代碼具有很高的參考價(jià)值。

- 開(kāi)源項(xiàng)目分享:如“OpenMIPS”、“tinyriscv”等在CSDN上常有解讀和移植教程。

- 注意點(diǎn):下載資源時(shí)需注意版權(quán)和適用性,最好結(jié)合官方文檔和書(shū)籍進(jìn)行理解,切勿直接復(fù)制粘貼。

- 開(kāi)源平臺(tái)與項(xiàng)目:

- GitHub/Gitee:搜索“RISC-V”、“CPU”、“FPGA”等關(guān)鍵詞,能找到大量開(kāi)源CPU核項(xiàng)目,如PicoRV32、SERV、香山開(kāi)源處理器等。這些項(xiàng)目的源碼、文檔和Issue討論是極佳的學(xué)習(xí)材料。

- OpenCores:一個(gè)著名的硬件開(kāi)源項(xiàng)目網(wǎng)站,包含大量從CPU到外設(shè)的IP核設(shè)計(jì)。

- 官方文檔與書(shū)籍:

- FPGA廠(chǎng)商手冊(cè):Xilinx、Intel(Altera)提供的官方設(shè)計(jì)指南、IP核文檔是權(quán)威參考。

- 經(jīng)典書(shū)籍:《計(jì)算機(jī)組成與設(shè)計(jì):硬件/軟件接口》(David Patterson & John Hennessy)、《CPU自制入門(mén)》、《Verilog HDL高級(jí)數(shù)字設(shè)計(jì)》等。

- 實(shí)踐建議:

- 由簡(jiǎn)入繁:從一個(gè)最簡(jiǎn)單的單周期、無(wú)流水線(xiàn)、支持少數(shù)幾條指令的CPU開(kāi)始,逐步增加指令、引入流水線(xiàn)、添加外設(shè)。

- 仿真驅(qū)動(dòng):堅(jiān)持“先仿真,后上板”的原則,利用仿真工具徹底驗(yàn)證每個(gè)模塊和整個(gè)系統(tǒng)。

- 善用工具:熟練掌握一種FPGA開(kāi)發(fā)工具和一種仿真調(diào)試工具。

- 參與社區(qū):在CSDN、電子工程世界、知乎等技術(shù)社區(qū)提問(wèn)和交流,許多棘手問(wèn)題可能已有前輩解決。

###

通過(guò)FPGA自主設(shè)計(jì)CPU并構(gòu)建計(jì)算機(jī),是一條充滿(mǎn)挑戰(zhàn)但收獲巨大的硬件學(xué)習(xí)路徑。它要求開(kāi)發(fā)者兼具數(shù)字電路知識(shí)、硬件描述語(yǔ)言技能和系統(tǒng)級(jí)思維。充分利用CSDN等平臺(tái)上的開(kāi)發(fā)文檔、源碼分享和社區(qū)經(jīng)驗(yàn),結(jié)合系統(tǒng)的理論學(xué)習(xí)與扎實(shí)的動(dòng)手實(shí)踐,任何有決心的開(kāi)發(fā)者都能逐步掌握這項(xiàng)技能,并最終打造出屬于自己的“芯”片與計(jì)算機(jī)系統(tǒng)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.qh008.com.cn/product/57.html

更新時(shí)間:2026-01-06 09:31:37